信息

概述

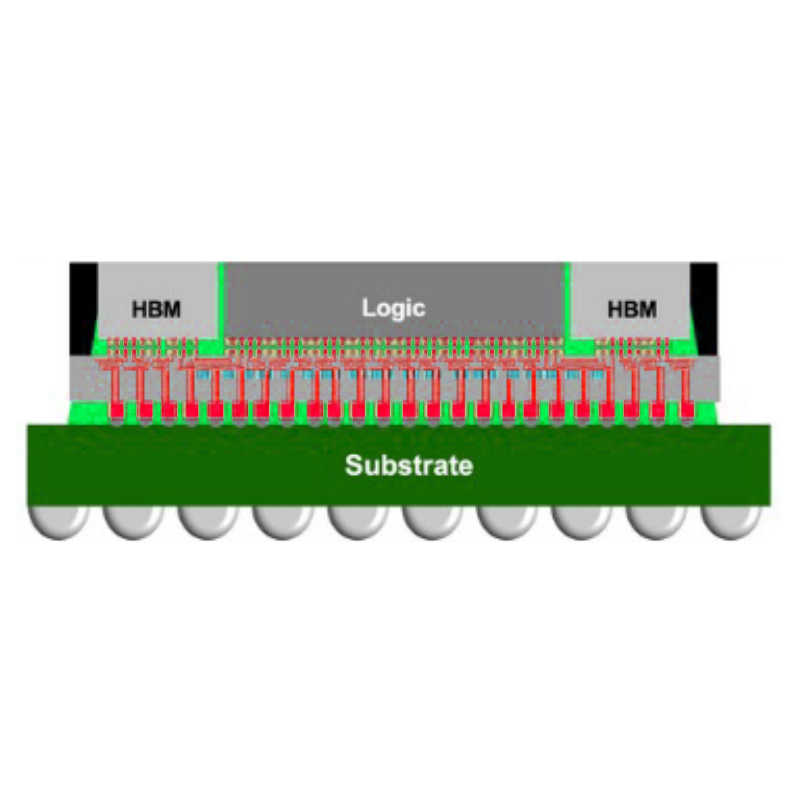

CoWoS-S

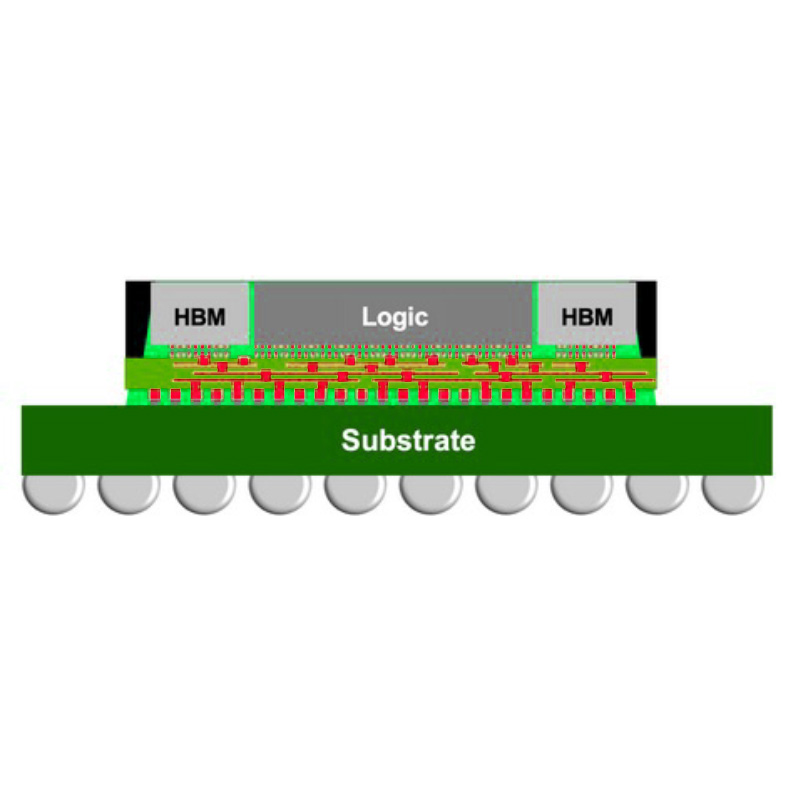

CoWoS-R

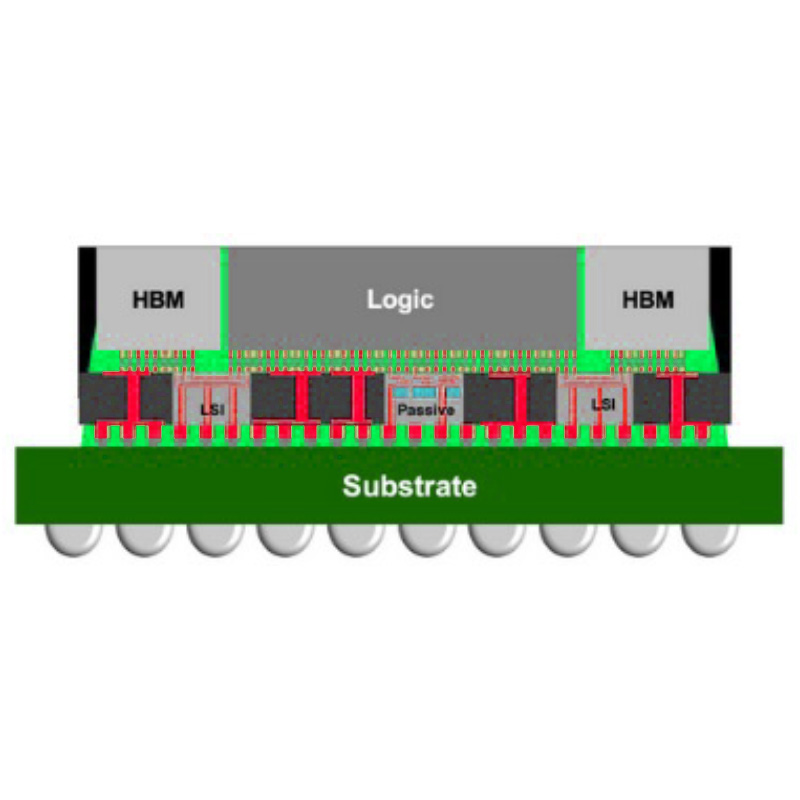

CoWoS-L

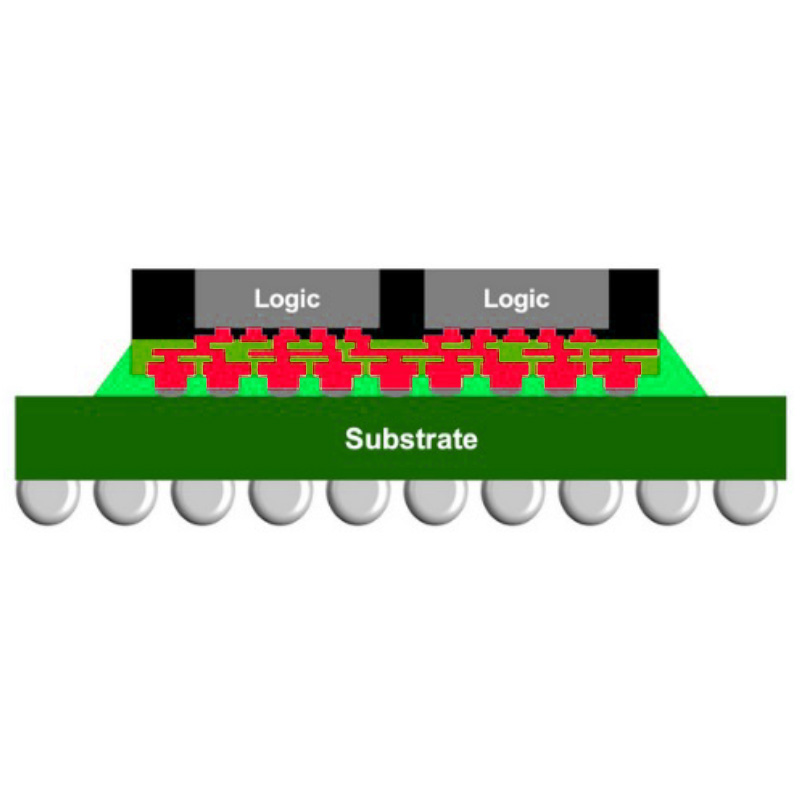

InFO-oS

TSMC-SoIC

System-on-Wafer (SoW)

先进封装技术 (Advanced Packaging Technology, APT) 的目的,是一种将多颗芯片整合于单一封装内的技术,采用 2.5D 晶粒对晶粒互连方式,例如硅中介层、重布线层 (RDL) 和 3D 晶粒迭晶粒。它可以提供高效能、低功耗和缩减尺寸等优势,以因应 AI、HPC、网络和 ADAS 等应用。

创意电子提供下列台积电先进封装技术的相关服务。

创意电子解决方案

创意电子 APT 平台

创意电子提供完善的先进封装解决方案,从中介层/RDL设计、SI/PI/热模拟、IP、封装和基板设计到量产,一应俱全。我们的专家团队拥有丰富经验,精通最先进的封装技术。

系统仿真

「芯片-封装-PCB」的协同设计和协同模拟签核,为确保先进产品效能和可靠性的一大关键,对 2.5D/3DIC 整合更是格外重要。创意电子的自有解决方案涵盖电子讯号和电源完整性、配电网络 (PDN)、系统热完整性,以及机械翘曲和应力协同仿真等层面。透过芯片配置、实体设计、凸块/焊球配置、I/O 讯号连接,以及时序预算优化等方式,全面提升产品效能。

完整的讯号 / 电源完整性和先进封装设计解决方案

- HBM 和 UCIe 高速互连设计

- 芯片、中介层、封装和电路板的功耗感知讯号完整性的协同优化

- 经硅验证,具备良好的电性设计裕度与眼图一致性对应

全系统电源完整性

- SoC 核心电源全系统 PDN IR 压降和 Ldi/dt 协同设计及签核

- 配电网络 (PDN) 预算设计和芯片上/芯片外去耦电容协同优化

- 电压波动和下降协同模拟及 Vpeak-peak 和 Vmin 特性分析

封装和系统热完整性 - 2D/2.5D/3D IC 设计

- 含芯片/小芯片/封装/系统协同优化的早期和签核阶段热评估

- 多封装拓扑设计和决策的热阻参数建模

- 紧凑的热模型产生和系统层级热能/冷却的协同开发

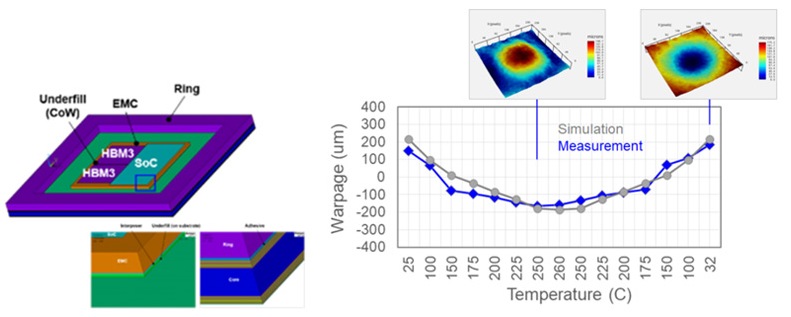

封装机械翘曲和应力 - 2D/2.5D/3D IC 设计

- 适用于不同封装解决方案的早期和签核阶段机械模拟

- 机械翘曲和应力风险评估及小芯片布局规划整合

- 含机械感知协同优化的芯片设计分析 (例如 BoM、层堆栈)

- 封装布线能力和实体设计协同优化的机械应力分析

创意电子 APT IP 产品组合

创意电子 APT IP 广获客户和业界推崇。这些荣获奖项肯定的 IP,在在展现了我们在 APT 领域的领先地位。此外,我们也能搭配旗下的统包 ASIC 设计服务,为 APT 客户提供 IP 客制化。

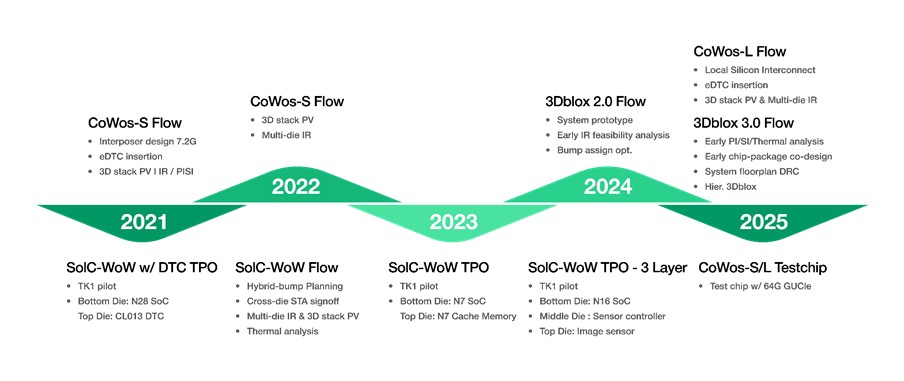

创意电子 APT 流程沿革