信息

可测试性设计

先进的DFT解决方案

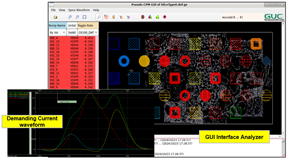

Power Aware Structure Planner

- GUI界面凸块电流预测

- 初期的功率感知DFT结构规划

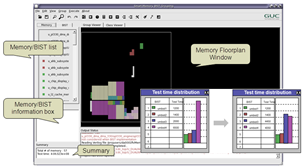

Smart SRAM BIST grouping

- 提供测试时间优化的实体感知自动分组

- 分组质量审查的GUI接口

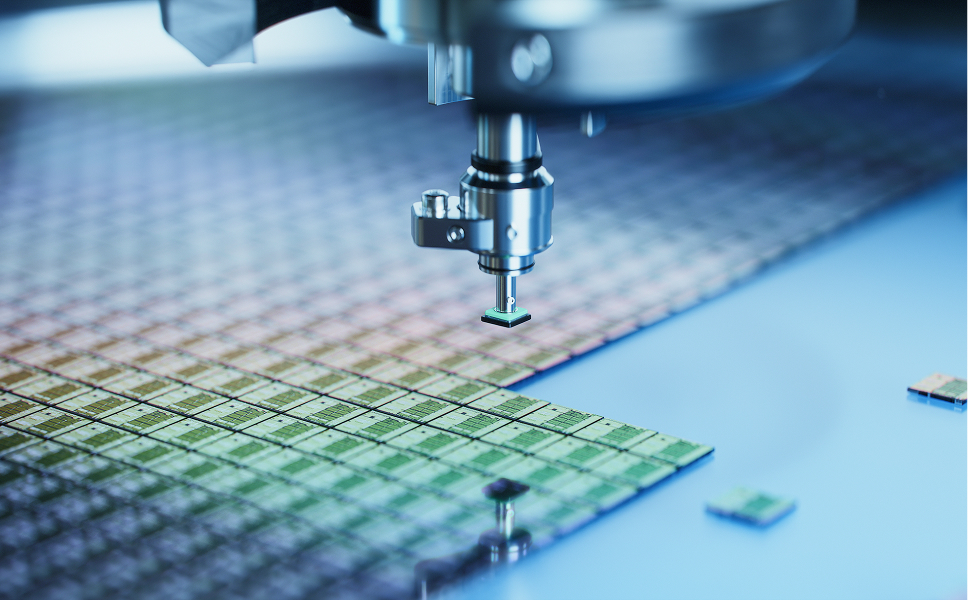

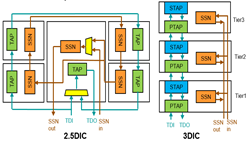

Multi-Die DFT

- IO配置和频率结构的设计须知

- 符合IEEE 1838或IEEE 1149.1规范的解决方案

- Streaming scan解决方案

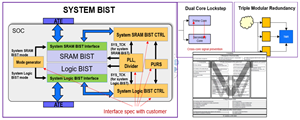

Functional Safety DFT

- 以功能测试规格为目标的系统内测试方法

- DFT实作的安全机制感知解决方案

- 低DPPM测试方法

Xn Mode & Memory Pooling

- 透过设计流程和样本须知,实现最大程度的样本压缩

- 大型设计中的ATE内存使用量减少83.5%

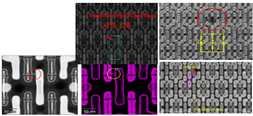

Physical Failure Analysis

- 藉由Scan/MBIST实体诊断,分析故障症状

- 藉由实体缺陷调查,进行制程改善

成功案例