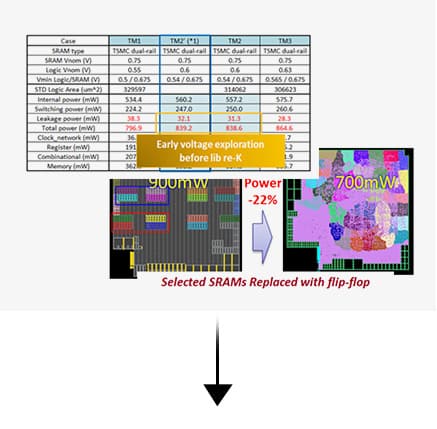

Design architecture exploration

- Predictable multi-objective PPA (leakage vs. dynamic power) early exploration

- Design activity driven, Vmin aware for memory and flip-flop concurrent configuration

Low voltage library characterization, customization

- GUC re-K serve for N5/N7/N12/N16 and mature processes since 2007

- Robust timing margin characterized for high variation at Vtgm condition

- GUC proprietary low power library benefit average 20% power reduction