With waveform

本网站使用cookies以提升您的使用体验及统计网路流量相关资料。继续使用本网站表示您同意我们使用cookies。我们的隐私权政策隐私权政策提供更多关于cookies使用及停用的相关资讯。

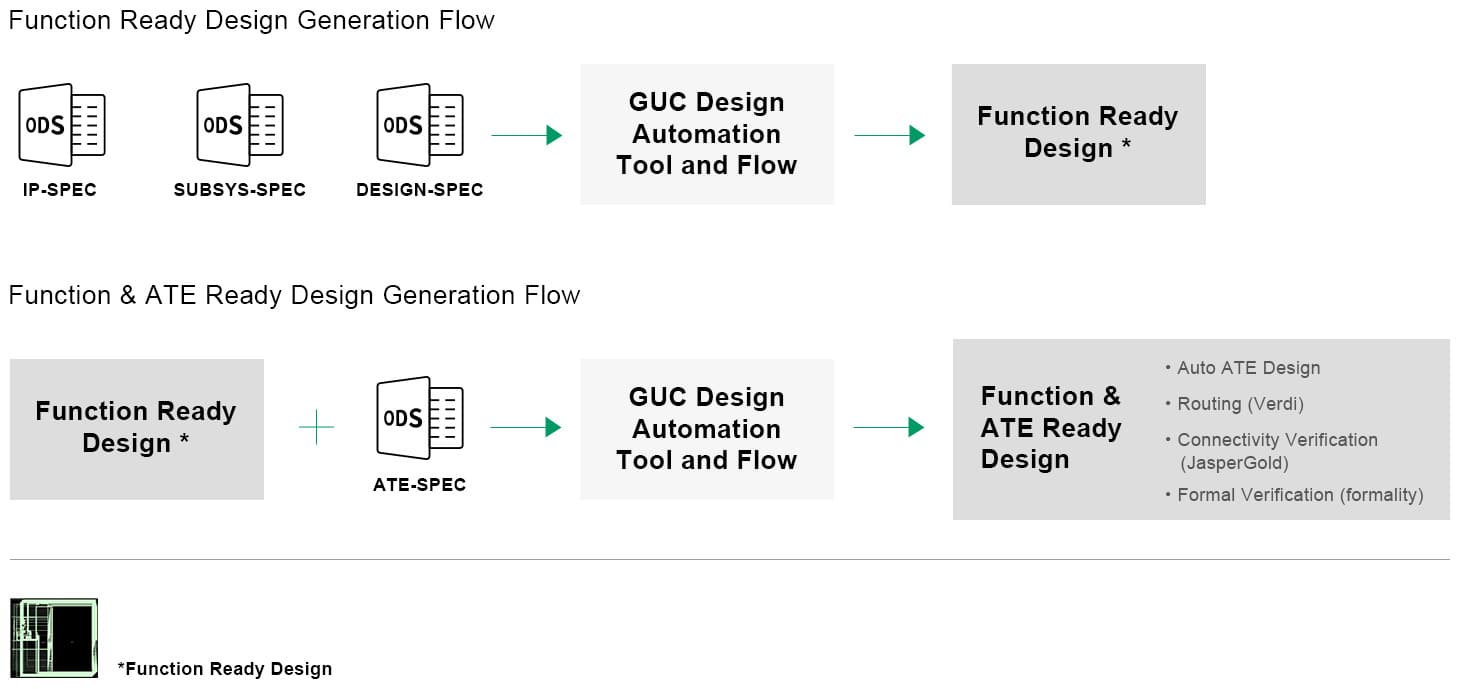

GUC provides full ‘spec-in’ design services, including SoC architecture design, system integration and verification, software development, power and performance evaluation, and system prototyping.

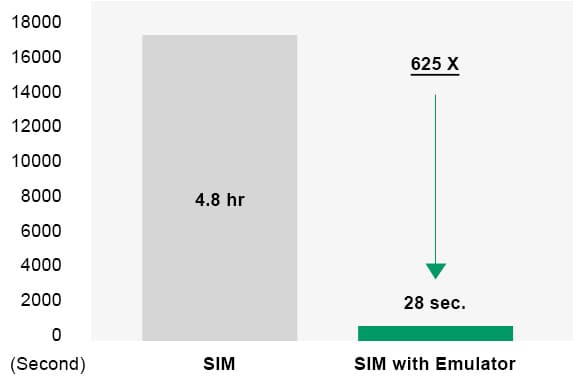

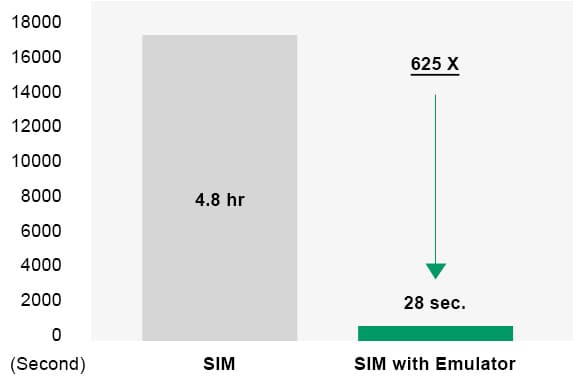

At the SoC design stage, GUC’s CPU (central processing unit) sub-system design platform helps customers evaluate the system’s performance. Using in-house design automation tools and flows, GUC can implement and integrate changes and reiterate the design shortly with high quality. The design verification methodology ensures optimum functionality of the SoC. The in-house emulation flow makes the simulation time around 700 times faster, and enables hardware and software co-development at the early design phase. The power profiling flow, when combined with GUC’s low power design methodology, can solve major SoC power and IR issues. With all these capabilities, GUC’s ‘spec-in’ services empower customers to achieve SoC first silicon success and faster time to market.

Emulator speeds up simulation time 700x, and enables software development at early design phase.

| Application | Process | Key features | Technical highlights |

|---|---|---|---|

| AI Vision | 6FF | Customer quad AI engine core LPDDR5, PCIeG4, DDR Cache | AI engine performance Complex HS IPSS |

| Networking | 12FFC | CA53x4, DDR4, PCIe3, SATA, Ethernet, USB | 5G networking bus matrix bandwidth optimization |

| AI Data Center | 12FFC | Customer AI engine, PCIeG4 | AI engine performance Complex HS IPSS |

| 8K Camera | 12FFC | CA35-MP4, CA5, Crypto, PCIeG3, HDMI2.0, DP1.4, DSI, MPHY, LPDDR4x, customer ISP | Critical bus timing DDR access efficiency Complex HS IPSS |

| 8K Camera | 12FFC | CA35-MP4/MP1, Crypto, LPDDR4x, customer ISP | Critical bus timing DDR access efficiency |

| Automotive | 16FFC | Customer engine, ADC MIPI, Serdes, LBIST | High speed ADC LBIST in automotive |

| HBM2/CoWoS | 16FF+ | CA72-MP2, HBM2, PCIeG4 | HBM, CA72 performance CoWoS flow |

| AI Vision | 28HPC+ | Customer AI engine, CA5, H264, PCIeG3, DSI/CSI | DDR access efficiency Bus matrix opt |