信息

旗舰型 SoC 设计解决方案

高效能运算(HPC)、人工智能(AI)与网络技术广泛应用于各种领域,例如数据中心运算、边缘运算与网络联机等。为了提高运算能力,往往需要内建更多的重复运算引擎,并尽可能扩大内存带宽。有鉴于此,HPC/AI/网络时代的设计复杂度和芯片尺寸都节节攀升。传统设计流程因为存在瓶颈,而难以因应此一复杂设计。创意电子拥有多款最先进的解决方案,包括多层的阶层式设计、阶层式时序签核、可预防高功率 IR 的 DFT、高速 IP 整合、整合HBM/D2D IP 子系统的 2.5D 封装 (CoWoS/InFO) 设计、SoIC 3D 堆栈设计签核标准,以及芯片封装系统 PI/SI 验证,可确保客户设计获致成功。创意电子凭借着此一完善解决方案,成功推出了众多旗舰型 SoC 设计。

适用于旗舰型 SoC 设计的全方位解决方案

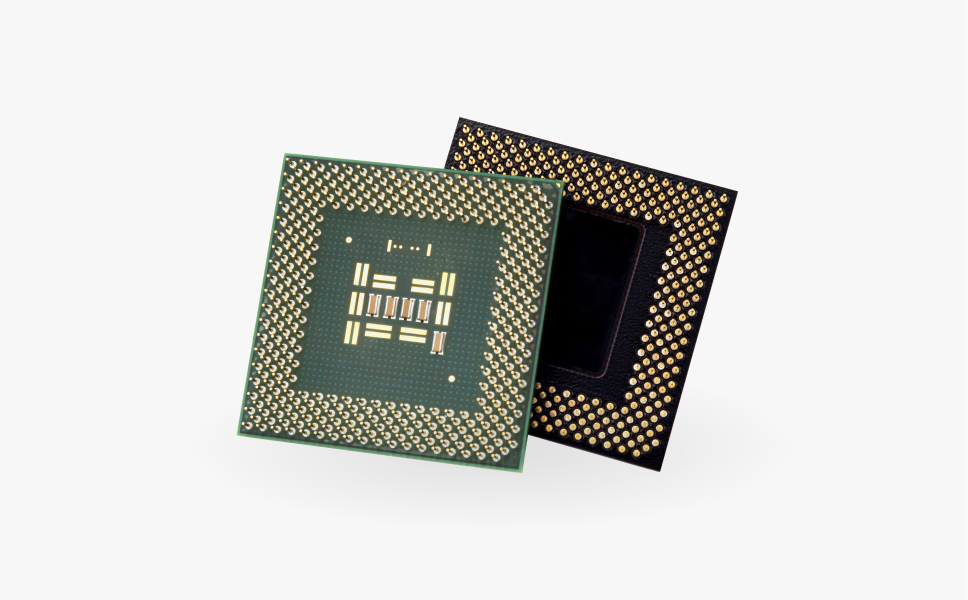

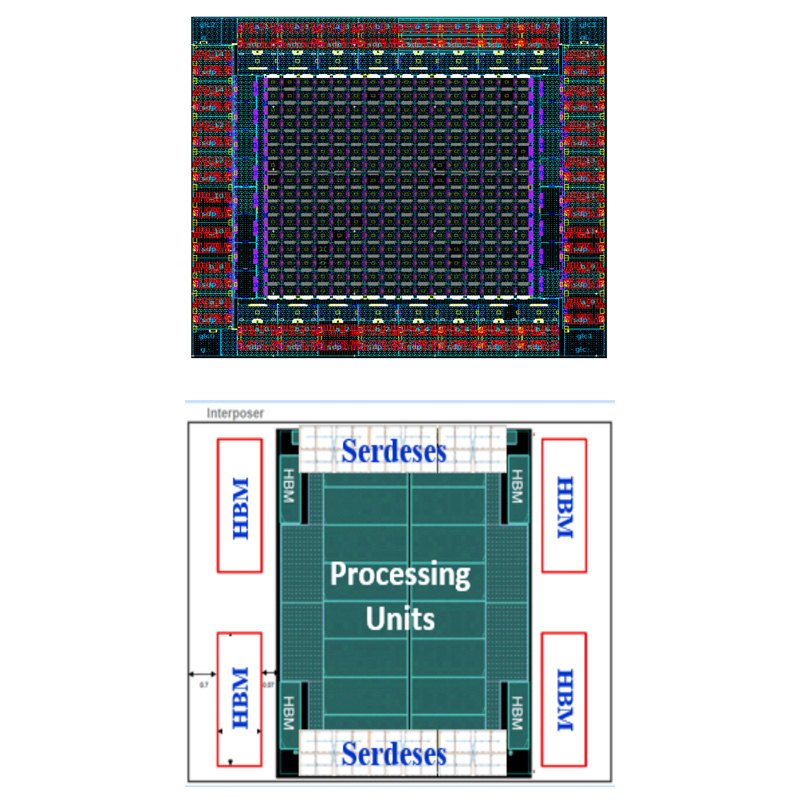

Complex IP Integration: SerDes, HBM, D2D

- 整合112G SerDes * 256 通道的十亿闸级设计

- CoWoS interposer with 4 HBM2E(3.2GHz)/HBM3E(8.4GHz), D2D G-link-fs(8~12GHz)

- 2.5D/3D CoWoS/SoIC IR/PI/SI/Thermal Integrity

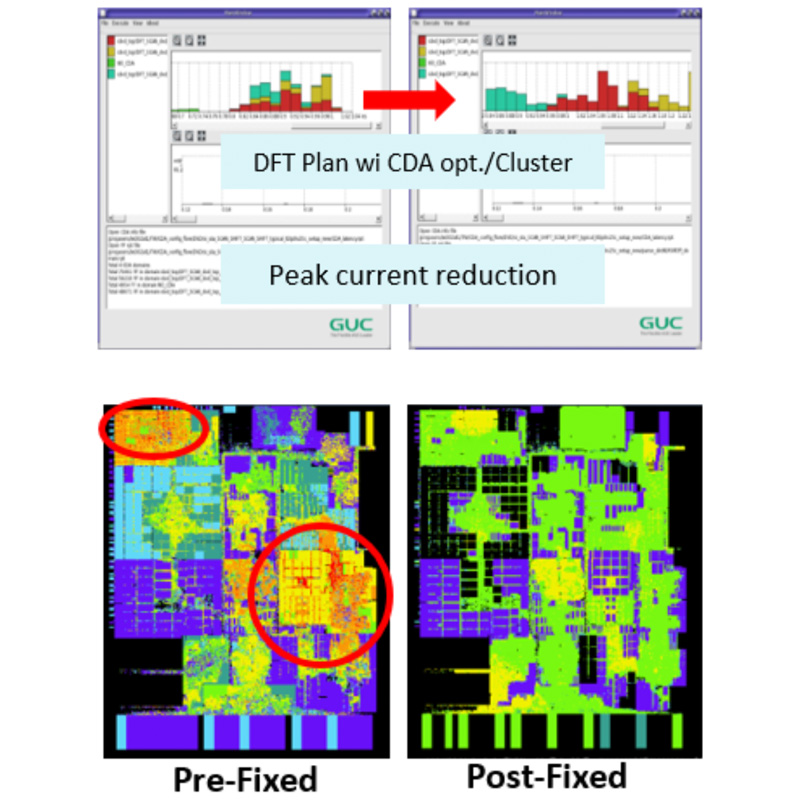

High power: IR/PI aware PDN, DFT plan

- 适用于早期 IR/PI 的峰值电流和 P/G 电源凸块配置可行性分析

- 电源凸块电流IR 感知的 DFT 架构规划,缓解 IR 并缩短 電源完整性驗證時程

- 透过分布式频率有益偏移降低峰值电流

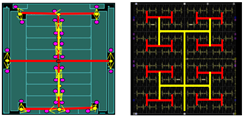

Advanced Clock Design

- 透过使用客制化大型频率驱动器和 CAC (频率延迟调整单元) 的 H-tree 减少时脉偏移和延迟:变异量OCV 最多可减少 60%,偏移可

- 减少至10ps

- 透过Clock mesh提升芯片效能

- 在 TOP 信道中使用数据流导向的網路拓扑规划

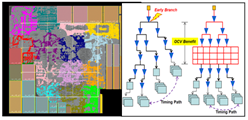

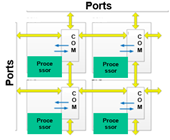

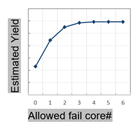

AI/HPC Faulty Core Identification

- 透过core wrapping and pin mux structure识别故障的核心

- 将针脚资源、测试功耗和测试时间纳入考虑

成功案例