信息

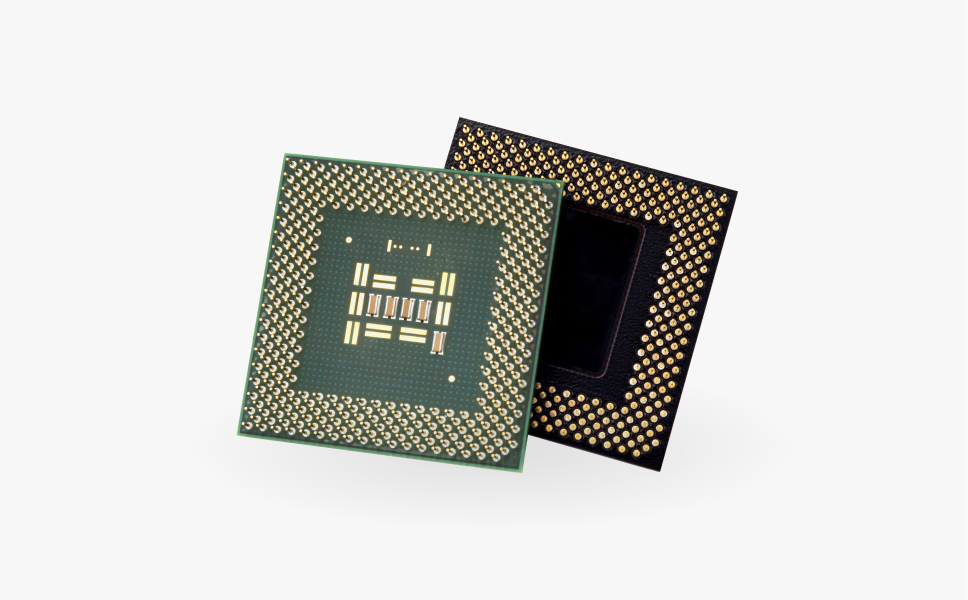

晶粒对晶粒 (GLink-2.5D) IP / 晶粒对晶粒 (UCIe-A) IP

创意电子的多晶粒互连 (GLink-2.5D/-3D) 和 UCIe IP,可提供领先全球的解决方案,以因应高效能运算、数据中心、人工智能和网络等封装应用中的高带宽、低功耗、低延迟的多通道互连。

GLink-2.5D IP 可利用并行总线上的单端讯号来搭配 DDR 频率,以进行转送。如此就能实现每针脚高达 8/16Gbps 的速度,在台积电 RDL 架构的 InFO (整合型扇出) 或 CoWoS (Chip-on-Wafer-on-Substrate) 上的每位功耗仅 0.25pJ。单一(Slice)具有 32 个全双工通道,而单一物理层具有 8 个(Slice),最大带宽可达 2/4Tbps。在最先进的 GLink 版本中,单一(Slice)具有 56 个全双工通道,而单一物理层则具有 8 个(Slice),最大带宽可达 7.5Tbps。

创意电子运用累积多年且横跨多代的深厚 GLink-2.5D 经验,大举推动 UCIe IP 发展。创意电子的 UCIe 32G IP 符合 UCIe 标准,可提供领先业界的每通道 32G 晶粒对晶粒互连,藉此实现全双工的 5+ Tbps/mm 最佳边界效率。新一代 UCIe LP 40G 甚至可突破 UCIe 的最高速度,以满足 AI/HPC/xPU/网络应用所需。UCIe LP 40G 小芯片接口提供领先业界的带宽密度,每毫米晶粒边缘可达 1,645 GB/s。此 IP 支持高达 40Gbps 的任何速度,并采用自适应电压调变 (AVS) 技术来降低供电电压,能在满足所需速度时达到 2 倍的能源效率提升。为了支持 SoIC-X 面对面堆栈,创意电子也提供 UCIe LP/Up IP,也就是用于 SoIC-X 底部晶粒的面朝上 IP。

UCIe Consortium 正提议扩充 UCIe 规格,以实现更高的数据速率,从而因应生成式 AI 趋势带动的带宽和效能急速成长。创意电子率先开发 UCIe 64G 版本,而解决方案预计将于 2025 年第 4 季推出,提供给创意电子客户。