With waveform

本網站使用cookies以提昇您的使用體驗及統計網路流量相關資料。繼續使用本網站表示您同意我們使用cookies。我們的隱私權政策隱私權政策提供更多關於cookies使用及停用的相關資訊。

創意電子提供完整「專案規格制定」(spec-in) 設計服務,包括 SoC(系統單晶片) 架構設計、系統整合與驗證、軟體開發、功耗與效能評估,以及系統原型製作等。

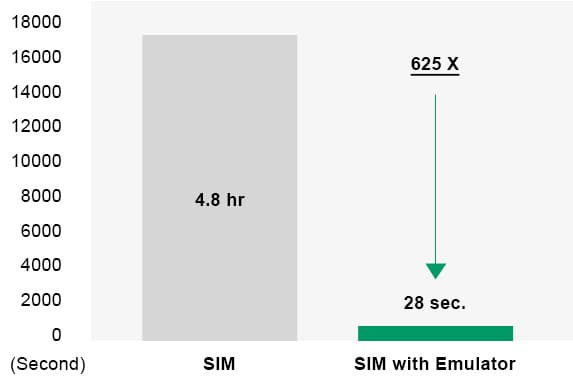

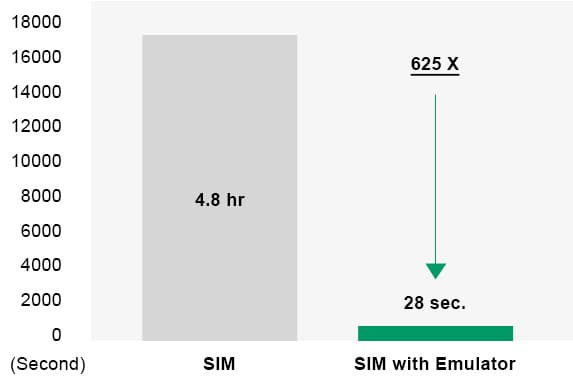

另外,創意電子的 CPU (中央處理器) 子系統設計平台,可協助客戶在SoC設計階段評估系統的效能。而運用內部的設計自動化工具與流程,我們可以迅速實作與整合變更,並重複使用設計。我們所採用的設計驗證方法,能確保SoC發揮最佳功能;自行開發的模擬流程,更可將模擬時間加快約700倍,在設計初期階段就能實現軟硬體的協同開發。此外,結合功耗分析流程與低功耗設計方法,更可有效解決主要的SoC功耗和IR-Drop(電壓降)問題。結合所有以上功能,創意電子的「專案規格制定」服務可協助客戶實現SoC第一次矽晶設計就成功的目標,並加快上市時程。

模擬器(Emulator)可將模擬時間縮短約700倍,並在前期設計階段就可以進行軟體開發。

| 應用 | 製程 | 重要規格 | 技術亮點 |

|---|---|---|---|

| AI Vision | 6FF | Customer quad AI engine core LPDDR5, PCIeG4, DDR Cache | AI engine performance Complex HS IPSS |

| Networking | 12FFC | CA53x4, DDR4, PCIe3, SATA, Ethernet, USB | 5G networking bus matrix bandwidth optimization |

| AI Data Center | 12FFC | Customer AI engine, PCIeG4 | AI engine performance Complex HS IPSS |

| 8K Camera | 12FFC | CA35-MP4, CA5, Crypto, PCIeG3, HDMI2.0, DP1.4, DSI, MPHY, LPDDR4x, customer ISP | Critical bus timing DDR access efficiency Complex HS IPSS |

| 8K Camera | 12FFC | CA35-MP4/MP1, Crypto, LPDDR4x, customer ISP | Critical bus timing DDR access efficiency |

| Automotive | 16FFC | Customer engine, ADC MIPI, Serdes, LBIST | High speed ADC LBIST in automotive |

| HBM2/CoWoS | 16FF+ | CA72-MP2, HBM2, PCIeG4 | HBM, CA72 performance CoWoS flow |

| AI Vision | 28HPC+ | Customer AI engine, CA5, H264, PCIeG3, DSI/CSI | DDR access efficiency Bus matrix opt |