資訊

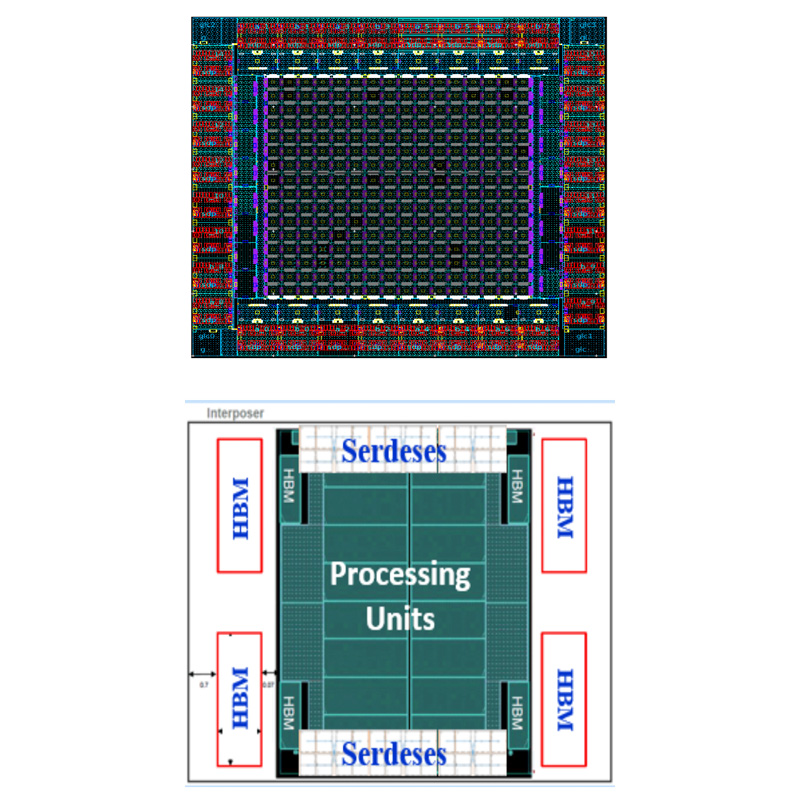

高效能運算(HPC)、人工智慧(AI)與網路技術廣泛應用於各種領域,例如資料中心運算、邊緣運算與網路連線等。為了提高運算能力,往往需要內建更多的重複運算引擎,並盡可能擴大記憶體頻寬。有鑑於此,HPC/AI/網路時代的設計複雜度和晶片尺寸都節節攀升。傳統設計流程因為存在瓶頸,而難以因應此一複雜設計。創意電子擁有多款最先進的解決方案,包括多層的階層式設計、階層式時序簽核、可預防高功率 IR 的 DFT、高速 IP 整合、整合隨附 HBM/D2D IP 子系統的 2.5D 封裝 (CoWoS/InFO) 設計、SoIC 3D 堆疊設計簽核標準,以及晶片封裝系統 PI/SI 驗證,可確保客戶設計獲致成功。創意電子憑藉著此一完善解決方案,成功推出了眾多旗艦型 SoC 設計。

適用於旗艦型 SoC 設計的全方位解決方案

Complex IP Integration: SerDes, HBM, D2D

- 隨附整合 112G SerDes * 256 通道的十億閘級設計

- CoWoS interposer with 4 HBM2E(3.2GHz)/HBM3E(8.4GHz), D2D G-link-fs(8~12GHz)

- 2.5D/3D CoWoS/SoIC IR/PI/SI/Thermal Integrity

High power: IR/PI aware PDN, DFT plan

- 適用於早期 IR/PI 的峰值電流和 P/G 電源凸塊配置可行性分析

- 隨附電源凸塊電流的 IR 感知的 DFT 計畫架構規劃,可緩解 IR 並縮短 電源完整性驗證時程TAT

- 透過分散式時脈有益偏移降低峰值電流

Advanced Clock Design

- 透過隨附使用客製化大型時脈驅動器和 CAC (時脈延遲調整單元) 的 H-tree, 減少時脈偏移和延遲:變異量 OCV 最多可減少 60%,偏移最多可減少至 10ps

- 透過Clock mesh提升晶片效能

- 在 TOP 通道中使用資料流導向的網路時脈拓撲規劃

AI/HPC Faulty Core Identification

- 透過core wrapping and pin mux structure識別故障的核心

- 將針腳資源、測試功耗和測試時間納入考量

成功案例