資訊

封裝設計服務

創意電子為領先業界的先進封裝解決方案供應商,在複雜的封裝設計解決方案領域具有傑出的專業能力,我們的封裝設計能力可因應廣泛的封裝類型和先進技術,包括:

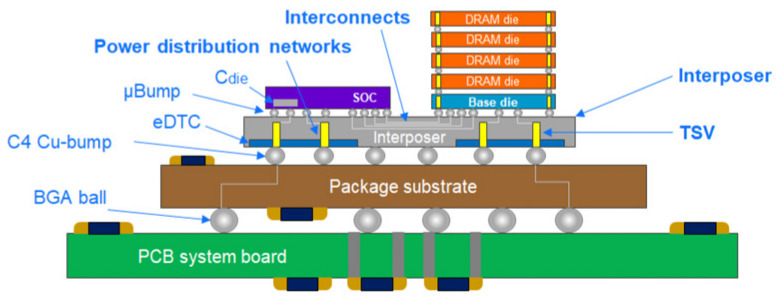

- 2.5D (CoWoS 和 InFO_oS) 和 3D (SoIC) 封裝專業能力,可實現更高的整合密度並增強效能

- SIP (系統封裝)、MCM (多晶片模組)、Flip-Chip (覆晶封裝)和 FCCSP (覆晶晶片級封裝) 的專業設計能力,可滿足高效能應用要求

- 可提供以導線架為基礎的封裝 (例如 QFN、QFP 等),提供具成本競爭力的解決方案

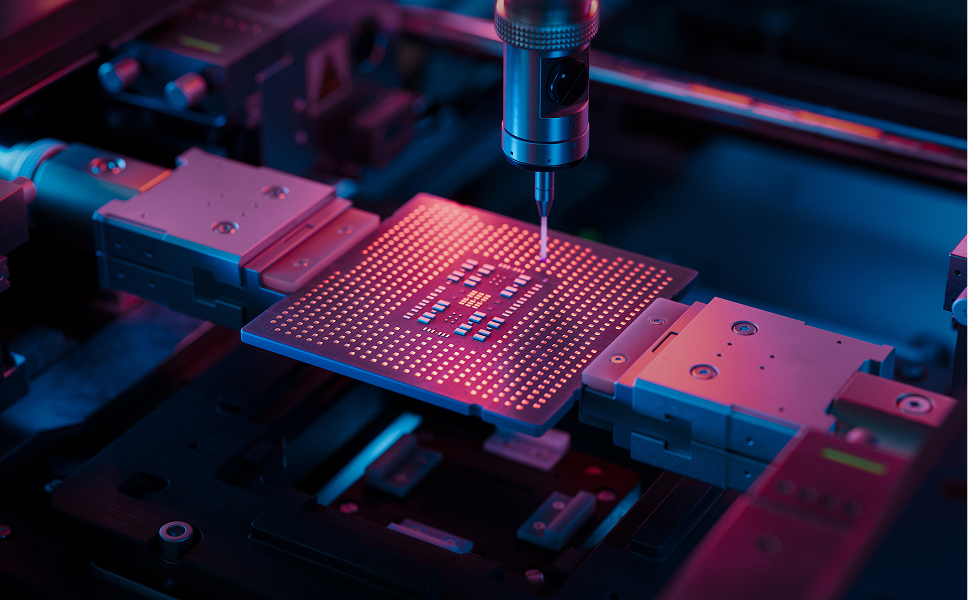

封裝和機板設計服務

自有團隊擁有卓越的封裝和基板設計能力,可提供最新解決方案來滿足先進封裝的需求。

- 先進的封裝設計和可行性評估。

- 選擇最佳封裝和基板材料以滿足性能、散熱和成本的要求。

- 最佳化基板疊層數目以實現效能、成本和可製造性的平衡。

- 最佳化基板設計以確保訊號和電源完整性。

- 最佳化基板以實現高效率散熱。

- 高密度佈局連接和焊球分配,實現高 I/O 密度的緊湊設計並縮小封裝尺寸。

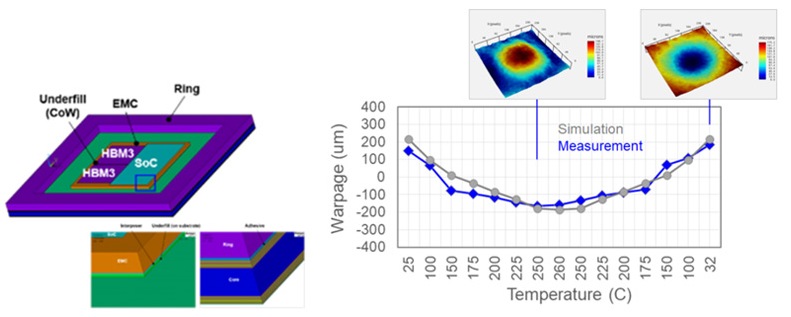

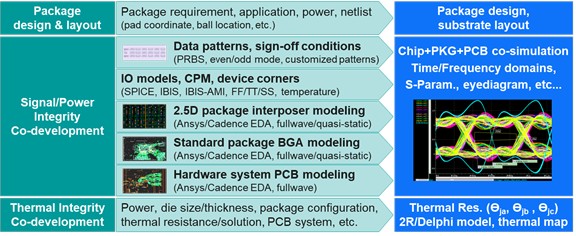

系統模擬

「晶片-封裝-電路板」的協同設計和協同模擬,為確保先進產品效能和可靠性的一大關鍵,對 2.5D/3DIC 的整合更是格外重要。創意電子的自有解決方案涵蓋電子訊號和電源完整性、配電網路 (PDN)、系統散熱完整性,以及機械翹曲和應力協同模擬等層面。透過佈局規劃、實體設計、凸塊/焊球配置、I/O 訊號連接,以及時序預算最佳化等方式,全面提升產品效能。

完整的訊號/電源完整性和先進封裝設計解決方案

- HBM 和 UCIe 高速互連設計

- 晶片、中介層、封裝和電路板的協同最佳化訊號完整性設計

- 經過矽驗證,具備良好的電氣特性設計與眼圖一致性對應

全系統電源完整性

- 全系統SoC 核心電源IR 壓降和 Ldi/dt 協同設計

- 配電網路 (PDN)設計和 on-chip/off-chip 去耦電容最佳化設計

- 電壓波動和電壓下降協同模擬及 Vpeak-peak 和 Vmin 特性分析

封裝和系統散熱完整性 - 2D/2.5D/3D IC 設計

- 晶片/小晶片/封裝/系統的協同最佳化散熱評估

- 多封裝拓撲設計和熱阻參數建模

- 產生緊湊的熱模型和系統層級的散熱/冷卻協同開發

封裝機械翹曲和應力 - 2D/2.5D/3D IC 設計

- 適用於不同封裝解決方案的機械模擬

- 機械翹曲和應力風險評估及小晶片佈局規劃整合

- 含機械應力感知協同最佳化的晶片設計分析 (例如 BoM、層堆疊)

- 封裝佈線能力和實體設計協同最佳化的機械應力分析