GUC Announces Adoption of HBM3E IP by CSP Data Center

News Content:

Hsinchu, Taiwan – September 24th, 2024 – Global Unichip Corp. (GUC), the Advanced ASIC Leader, is pleased to announce that its 3nm HBM3E Controller and PHY IP have been adopted by a leading Cloud Service Provider (CSP) and several High-Performance Computing (HPC) solution providers. This cutting-edge ASIC is expected to tape out this year and will feature the latest 9.2Gbps HBM3E memory technology.

While GUC’s HBM3E Controller and PHY IPs are being adopted by many AI companies, GUC is actively collaborating with HBM providers, like Micron, and developing HBM4 IP for next-generation AI ASICs.

GUC HBM3E IP Highlights

- Proven across TSMC advanced process technologies: Ready on the TSMC N7/N6, N5/N4P, N3E/N3P processes.

- Silicon validated with all major HBM3 vendors

- Silicon validated on both TSMC CoWoS-S and CoWoS-R technologies: GUC designs eDTC for the TSMC CoWoS-S and IPD for the TSMC CoWoS-R to achieve best power integrity.

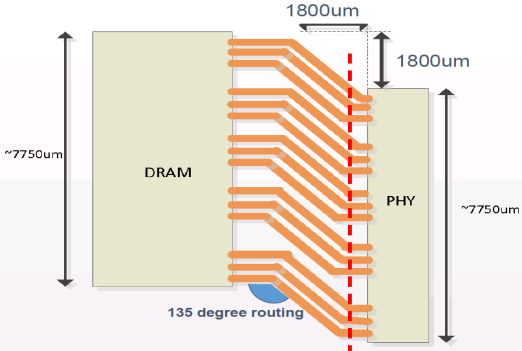

- Advanced Interposer Routing: Patented interposer layout to support angle routing with a Y-dimension offset while keeping best signal and power integrity.

- Built-In chiplet interconnect monitoring solution: GUC collaborates with proteanTecs and has integrated chiplet interconnect monitors into the HBM PHY. This feature enhances chiplet observability and reliability.

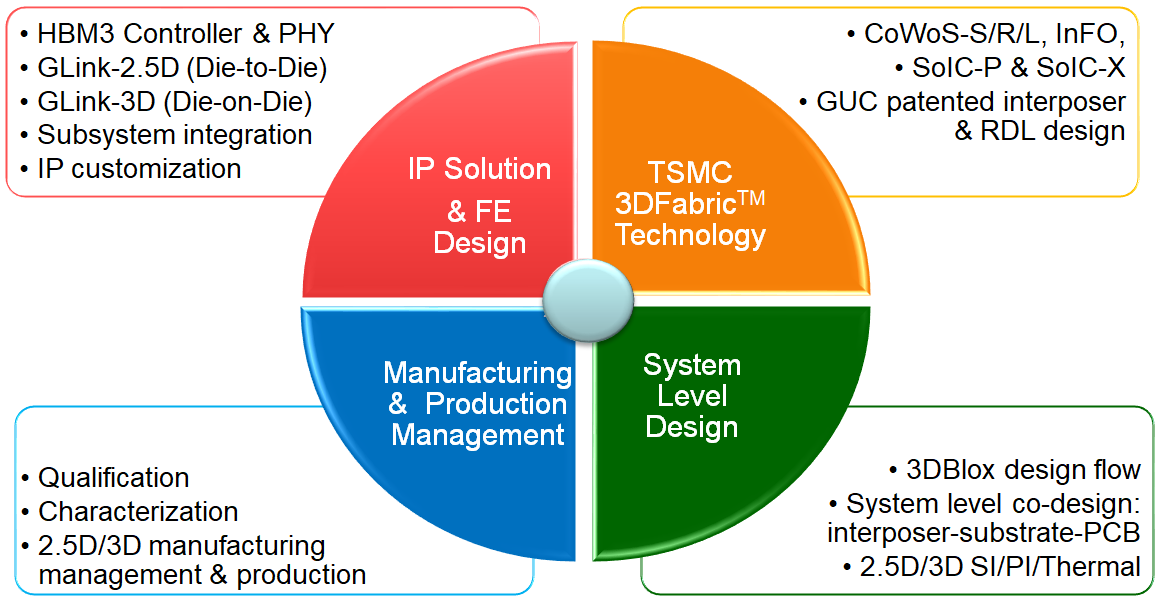

- Full 2.5/3D multi-die design service: GUC provides optional 2.5D and 3D service for HBM CoWoS ASIC platform design.

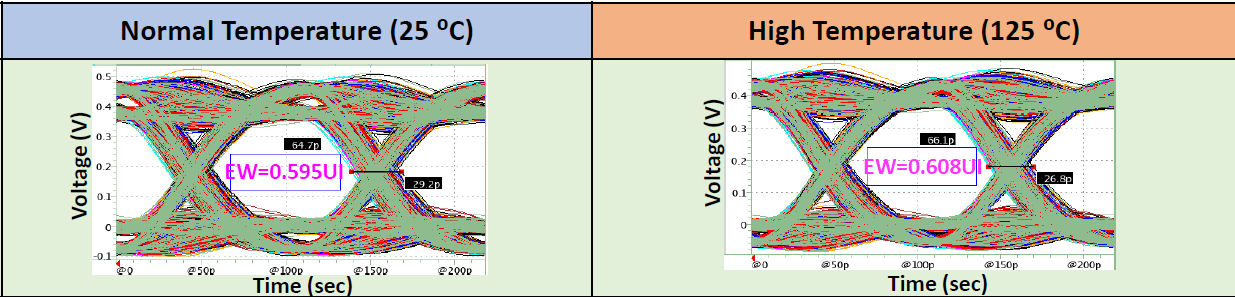

- Eye diagram of HBM3E 9.2G

- Interposer Angle Routing

- GUC provides total service for 2.5D/3D ASIC design

Collaborative efforts between GUC and Micron have demonstrated the GUC HBM3E IP with Micron’s HBM3E can achieve 9.2Gbps on both CoWoS-S and CoWoS-R technologies. The silicon results on GUC’s test chip show passing PI and SI results with excellent eye margin across temperature and voltage corners with Micron's HBM3E at these speeds. Additionally, GUC’s HBM3E IP when integrated with Micron's HBM3E timing parameters exhibit better effective bus utilization, further enhancing overall system performance.

“We are thrilled to see our HBM3E Controller and PHY IP being integrated in CSP and HPC ASICs.” said Aditya Raina, CMO of GUC. “This adoption underscores the robustness and advantages of our HBM3E solution, which is silicon-proven and validated across multiple advanced technologies and major vendors. We look forward to continuing our support for various applications, including AI, high-performance computing, networking, and automotive.”

“Memory is an integral part of AI servers and foundational to the performance and advancement of data center systems,” said Girish Cherussery, senior director of Micron's AI Solutions Group. “Micron’s best-in-class memory speeds and energy efficiency greatly benefit the increasing demands of Generative AI workloads, such as large language models like ChatGPT, sustaining the pace of AI growth."

For more information, please visit www.guc-asic.com or contact our sales representative directly (https://www.guc-asic.com/en/about-offices.php)