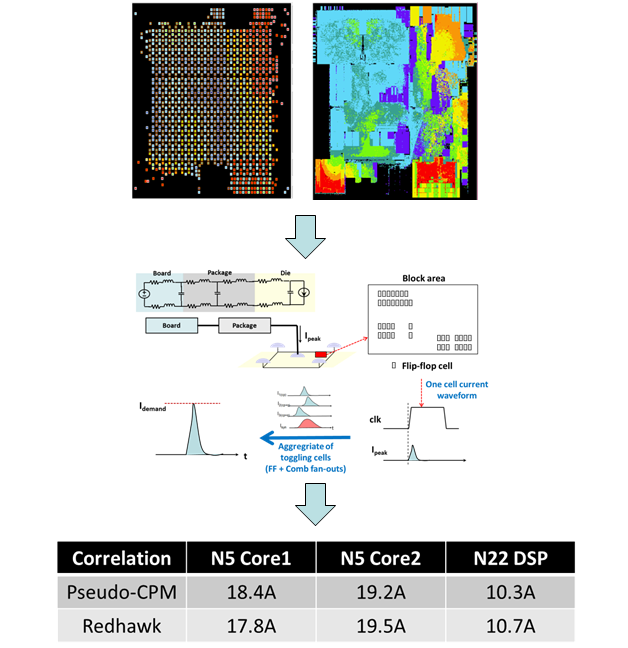

Early Stage IR Drop Prevention: GUC in-house Pseudo CPM (Chip Power Model) for P/G Bump Current Estimation

-

Challenge

P/G bump allocation and peak current distribution are critical for IR drop mitigation, especially in power domain edge region.

-

Methodology

-

Accurately estimate P/G bump peak current in early design stage, based on circuit multi-scenario activity and bump physical location.

-

Optimize P/G bump location, circuit design and toggle rate to reduce IR drop issue with customer.

-

Benefit

-

Enable the quick turn-around time in early design tuning to prevent the localized simultaneous toggle and insufficient bump allocation.

-

Serve the efficient DFT circuit topology optimization.

GUC 核心優勢

- Advanced Packaging Technology Leadership

- Design Engineering Excellence

- Customer Trusted Service