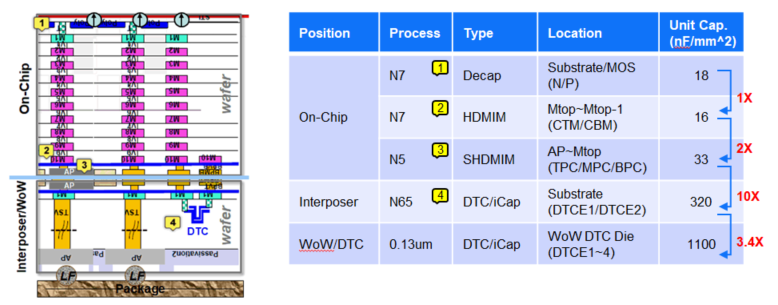

GUC Provides WoW DTC Solution for Better Decap to Improve Voltage Droop

For HPC chip design, the voltage droop becomes serious especially in advanced process nodes. To improve

the voltage droop, the decap is needed during chip implementation. There are several types of decap shown

in below figure.

Chip designers can choose suitable decap to meet their voltage droop spec. However the power

consumption of HPC chip becomes larger and larger, the decap value also becomes bigger and bigger. The

DTC of CoWoS-S interposer can provide 20X of unit decap density than N7 MIMcap (320nF/mm^2 vs

16nF/mm^2). Now the WoW DTC achieves 1100nF/mm^2 unit decap density which is 3.4X of interposer

DTC. GUC already successfully collaborated with customer to improve voltage droop by this WoW DTC

technology.

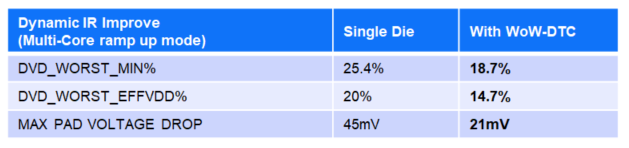

Success case of WoW-DTC

- Test vehicle taped out : Aug ’21

- Silicon validation : Effective dynamic IR drop mitigation 20% --> 14.7% for multi-core ramp-up

For more information, please contact your GUC sales representative directly or email guc_sales@guc

asic.com

GUC Core Strengths

- Advanced Packaging Technology Leadership

- Design Engineering Excellence

- Customer Trusted Service